# M32C/80 Series

Software Manual

RENESAS 16/32-BIT SINGLE-CHIP MICROCOMPUTER M16C FAMILY / M32C/80 SERIES

Before using this material, please visit our website to verify that this is the most updated document available.

Rev. 1.00

Revision date: May 31, 2006

#### Keep safety first in your circuit designs!

1. Renesas Technology Corp. puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- 1. These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corp. product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Renesas Technology Corp. or a third party.

- 2. Renesas Technology Corp. assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corp. without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor for the latest product information before purchasing a product listed herein.

- The information described here may contain technical inaccuracies or typographical errors. Renesas Technology Corp. assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

- Please also pay attention to information published by Renesas Technology Corp. by various means, including the Renesas Technology Corp. Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corp. assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corp. semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corp. or an authorized Renesas Technology Corp. product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corp. is necessary to reprint or reproduce in whole or in part these materials.

- 7. If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

- Any diversion or reexport contrary to the export control laws and regulations of Japan and/ or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corp. for further details on these materials or the products contained therein.

### **Using This Manual**

This manual is written for the M32C/80 Series software. This manual can be used for all types of MCUs having the M32C/80 Series CPU core.

The reader of this manual is expected to have the basic knowledge of electric and logic circuits and MCUs.

This manual consists of seven chapters. The following lists the chapters and sections to be referred to when you want to know details on some specific subject.

- To understand the outline of the M32C/80 Series and its features Chapter 1, "Overview"

- To understand the operation of each addressing mode.. Chapter 2, "Addressing Modes"

- To understand instruction functions

- To understand instruction code and cycles ...... Chapter 4, "Instruction Code/Number of Cycles"

- To understand calculation number of cycles Chapter 6, "Caluculation Number of Cycles"

This manual also contains quick references immediately after the Table of Contents. These quick references will help you quickly find the pages for the functions or instruction code/number of cycles you want to know.

- To find pages from mnemonic......Quick Reference in Alphabetic Order

- To find pages from mnemonic and addressing ...... Quick Reference by Addressing

A table of symbols, a glossary, and an index are appended at the end of this manual.

### **M16C Family Documents**

The following documents were prepared for the M16C Family.\*1

| Document         | Contents                                                                          |

|------------------|-----------------------------------------------------------------------------------|

| Shortsheet       | Hardware overview                                                                 |

| Datasheet        | Hardware overview and electrical characteristics                                  |

| Hardware Manual  | Hardware specifications (pin assignments, memory maps, peripheral specifications, |

|                  | electrical characteristics, timing charts)                                        |

| Software Manual  | Detailed description of assembly instructions and MCU performance of each         |

|                  | instruction                                                                       |

| Application note | -Application examples of peripheral functions                                     |

|                  | -Sample programs                                                                  |

|                  | -Introduction to the basic functions in the M16C Family                           |

|                  | -Programming method with Assembly and C languages                                 |

| Technical Update | Preliminary report about the specification of a product, a document, etc.         |

#### Note:

1. Before using this material, please visit our website to confirm that this is the most current document available.

# **Table of Contents**

| Cha  | apter 1 Overview                                |       |

|------|-------------------------------------------------|-------|

| 1.1  | Features of M32C/80 Series                      | 2     |

| 1.2  | Address Space                                   | 3     |

| 1.3  | Register Configuration                          | 4     |

| 1.4  | Flag Register (FLG)                             | 7     |

| 1.5  | Register Bank                                   | 9     |

| 1.6  | Internal State after Reset                      | 10    |

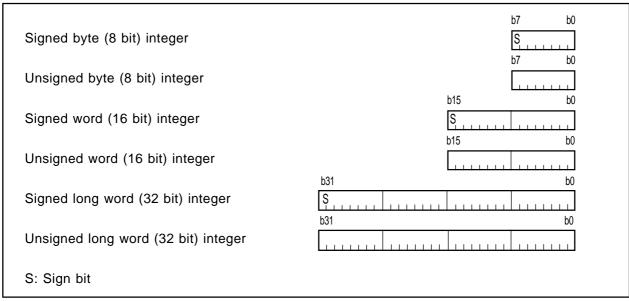

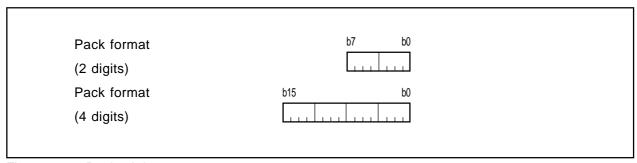

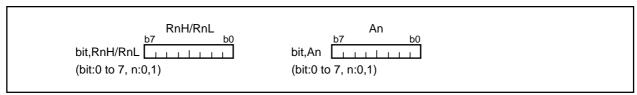

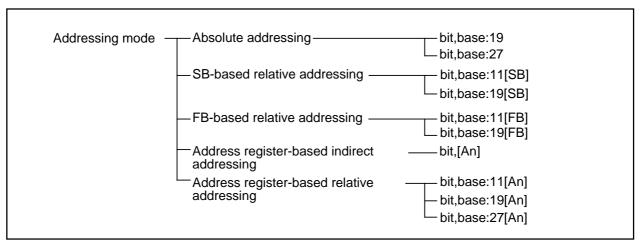

| 1.7  | Data Types                                      | 11    |

| 1.8  | Data Arrangement                                | 16    |

| 1.9  | Instruction Format                              | 18    |

| 1.10 | 0 Vector Table                                  | 19    |

| Cha  | apter 2 Addressing Modes                        |       |

|      | Addressing Modes                                |       |

|      | Guide to This Chapter                           |       |

|      | General Instruction Addressing                  |       |

|      | Indirect Instruction Addressing                 |       |

|      | Special Instruction Addressing                  |       |

|      | Bit Instruction Addressing                      |       |

| 2.7  | Read and write operations with 24-bit registers | 35    |

| Cha  | apter 3 Functions                               |       |

| 3.1  | Guide to This Chapter                           | 38    |

| 3.2  | Functions                                       | 43    |

| 3.3  | Index instructions                              | . 158 |

| Cha  | apter 4 Instruction Code/Number of Cycles       |       |

|      | Guide to This Chapter                           |       |

|      | Instruction Code/Number of Cycles               |       |

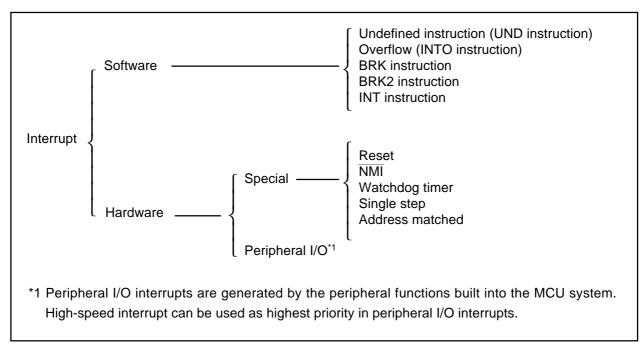

| Chapter 5 Interrupt                          |     |

|----------------------------------------------|-----|

| 5.1 Outline of Interrupt                     |     |

| 5.2 Interrupt Control                        | 312 |

| 5.3 Interrupt Sequence                       | 314 |

| 5.4 Return from Interrupt Routine            | 317 |

| 5.5 Interrupt Priority                       | 318 |

| 5.6 Multiple Interrupts                      | 318 |

| 5.7 Precautions for Interrupts               | 320 |

| 5.8 Exit from Stop Mode and Wait Mode        | 320 |

| Chapter 6 Calculation Number of Cycles       |     |

| 6.1 Instruction queue buffer                 | 322 |

| Chapter 7 Precautions                        |     |

| 7.1 String/Product-Sum Operation Instruction | 332 |

### **Quick Reference in Alphabetic Order**

| Mnemonic | See page for | See page for      | Mnemonic     | See page for | See page for      |

|----------|--------------|-------------------|--------------|--------------|-------------------|

|          | function     | instruction code/ |              | function     | instruction code/ |

|          |              | number of cycles  |              |              | number of cycles  |

| ABS      | 43           | 174               | DADD         | 74           | 208               |

| ADC      | 44           | 174               | DEC          | 75           | 210               |

| ADCF     | 45           | 176               | DIV          | 76           | 210               |

| ADD      | 46           | 176               | DIVU         | 77           | 212               |

| ADDX     | 48           | 183               | DIVX         | 78           | 213               |

| ADJNZ    | 49           | 185               | DSBB         | 79           | 215               |

| AND      | 50           | 186               | DSUB         | 80           | 217               |

| BAND     | 52           | 188               | ENTER        | 81           | 219               |

| BCLR     | 53           | 188               | EXITD        | 82           | 219               |

| BITINDEX | 54           | 189               | EXTS         | 83           | 220               |

| BM Cnd   | 55           | 190               | EXTZ         | 84           | 222               |

| BMEQ/Z   | 55           | 190               | FCLR         | 85           | 223               |

| BMGE     | 55           | 190               | FREIT        | 86           | 223               |

| BMGEU/C  | 55           | 190               | FSET         | 87           | 224               |

| BMGT     | 55           | 190               | INC          | 88           | 225               |

| BMGTU    | 55           | 190               | INDEXB       | 89           | 225               |

| BMLE     | 55           | 190               | INDEXBD      | 89           | 226               |

| BMLEU    | 55           | 190               | INDEXBS      | 89           | 226               |

| BMLT     | 55           | 190               | INDEXL       | 89           | 227               |

| BMLTU/NC | 55           | 190               | INDEXLD      | 89           | 227               |

| BMN      | 55           | 190               | INDEXLS      | 89           | 228               |

| BMNE/NZ  | 55           | 190               | INDEXW       | 89           | 228               |

| BMNO     | 55           | 190               | INDEXWD      | 89           | 229               |

| ВМО      | 55           | 190               | INDEXWS      | 89           | 229               |

| BMPZ     | 55           | 190               | INT          | 90           | 230               |

| BNAND    | 56           | 192               | INTO         | 91           | 230               |

| BNOR     | 57           | 192               | J <i>Cnd</i> | 92           | 231               |

| BNOT     | 58           | 193               | JEQ/Z        | 92           | 231               |

| BNTST    | 59           | 193               | JGE          | 92           | 231               |

| BNXOR    | 60           | 194               | JGEU/C       | 92           | 231               |

| BOR      | 61           | 194               | JGT          | 92           | 231               |

| BRK      | 62           | 195               | JGTU         | 92           | 231               |

| BRK2     | 63           | 195               | JLE          | 92           | 231               |

| BSET     | 64           | 196               | JLEU         | 92           | 231               |

| BTST     | 65           | 196               | JLT          | 92           | 231               |

| BTSTC    | 66           | 197               | JLTU/NC      | 92           | 231               |

| BTSTS    | 67           | 198               | JN           | 92           | 231               |

| BXOR     | 68           | 198               | JNE/NZ       | 92           | 231               |

| CLIP     | 69           | 199               | JNO          | 92           | 231               |

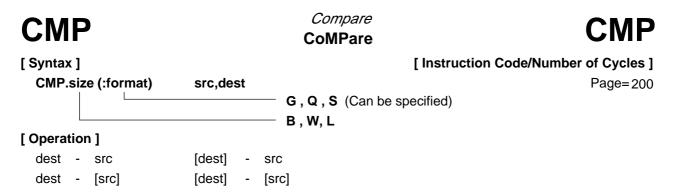

| CMP      | 70           | 200               | JO           | 92           | 231               |

| CMPX     | 72           | 206               | JPZ          | 92           | 231               |

| DADC     | 73           | 206               |              | ·            |                   |

### **Quick Reference in Alphabetic Order**

| Mnemonic       | See page for | See page for      | Mnemonic      | See page for | See page for      |

|----------------|--------------|-------------------|---------------|--------------|-------------------|

|                | function     | instruction code/ |               | function     | instruction code/ |

|                |              | number of cycles  |               |              | number of cycles  |

| JMP            | 93           | 231               | SBB           | 130          | 277               |

| JMPI           | 94           | 233               | SBJNZ         | 131          | 279               |

| JMPS           | 95           | 234               | SC <i>cnd</i> | 132          | 280               |

| JSR            | 96           | 235               | SCEQ/Z        | 132          | 280               |

| JSRI           | 97           | 236               | SCGE          | 132          | 280               |

| JSRS           | 98           | 237               | SCGEU/C       | 132          | 280               |

| LDC            | 99           | 237               | SCGT          | 132          | 280               |

| LDCTX          | 100          | 240               | SCGTU         | 132          | 280               |

| LDIPL          | 101          | 241               | SCLE          | 132          | 280               |

| MAX            | 102          | 241               | SCLEU         | 132          | 280               |

| MIN            | 103          | 243               | SCLT          | 132          | 280               |

| MOV            | 104          | 245               | SCLTU/NC      | 132          | 280               |

| MOVA           | 106          | 254               | SCN           | 132          | 280               |

| MOV <i>Dir</i> | 107          | 255               | SCNE/NZ       | 132          | 280               |

| MOVHH          | 107          | 255               | SCNO          | 132          | 280               |

| MOVHL          | 107          | 255               | SCPZ          | 132          | 280               |

| MOVLH          | 107          | 255               | SCMPU         | 133          | 281               |

| MOVLL          | 107          | 255               | SHA           | 134          | 282               |

| MOVX           | 108          | 257               | SHANC         | 135          | 284               |

| MUL            | 109          | 257               | SHL           | 136          | 285               |

| MULEX          | 110          | 260               | SHLNC         | 137          | 288               |

| MULU           | 111          | 260               | SIN           | 138          | 288               |

| NEG            | 112          | 263               | SMOVB         | 139          | 289               |

| NOP            | 113          | 263               | SMOVF         | 140          | 289               |

| NOT            | 114          | 264               | SMOVU         | 141          | 290               |

| OR             | 115          | 264               | SOUT          | 142          | 290               |

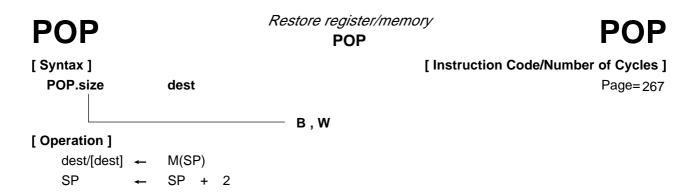

| POP            | 117          | 267               | SSTR          | 143          | 291               |

| POPC           | 118          | 267               | STC           | 144          | 291               |

| POPM           | 119          | 268               | STCTX         | 145          | 293               |

| PUSH           | 120          | 269               | STNZ          | 146          | 293               |

| PUSHA          | 121          | 271               | STZ           | 147          | 294               |

| PUSHC          | 122          | 271               | STZX          | 148          | 294               |

| PUSHM          | 123          | 272               | SUB           | 149          | 295               |

| REIT           | 124          | 273               | SUBX          | 151          | 299               |

| RMPA           | 125          | 273               | TST           | 152          | 301               |

| ROLC           | 126          | 274               | UND           | 154          | 303               |

| RORC           | 127          | 274               | WAIT          | 155          | 303               |

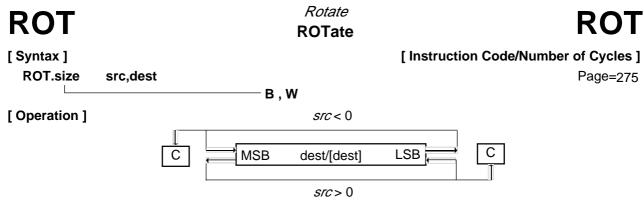

| ROT            | 128          | 275               | XCHG          | 156          | 304               |

| RTS            | 129          | 276               | XOR           | 157          | 304               |

### **Quick Reference by Function**

| Function     | Mnemonic      | Content                             | See page for | See page for      |

|--------------|---------------|-------------------------------------|--------------|-------------------|

|              |               |                                     | function     | instruction code/ |

|              |               |                                     |              | number of cycles  |

| Transfer     | MOV           | Transfer                            | 104          | 245               |

|              | MOVA          | Transfer effective address          | 106          | 254               |

|              | MOVDir        | Transfer 4-bit data                 | 107          | 255               |

|              | MOVX          | Transfer extend sign                | 108          | 257               |

|              | POP           | Restore register/memory             | 117          | 267               |

|              | POPC          | Restore control register            | 118          | 267               |

|              | POPM          | Restore multiple registers          | 119          | 268               |

|              | PUSH          | Save register/memory/immediate data | 120          | 269               |

|              | PUSHA         | Save effective address              | 121          | 271               |

|              | PUSHM         | Save multiple registers             | 123          | 272               |

|              | STNZ          | Conditional transfer                | 146          | 293               |

|              | STZ           | Conditional transfer                | 147          | 294               |

|              | STZX          | Conditional transfer                | 148          | 294               |

|              | XCHG          | Exchange                            | 156          | 304               |

| Bit          | BAND          | Logically AND bits                  | 52           | 188               |

| manupulation | BCLR          | Clear bit                           | 53           | 188               |

|              | BITINDEX      | Bit index                           | 54           | 189               |

|              | BM <i>Cnd</i> | Conditional bit transfer            | 55           | 190               |

|              | BNAND         | Logically AND inverted bits         | 56           | 192               |

|              | BNOR          | Logically OR inverted bits          | 57           | 192               |

|              | BNOT          | Invert bit                          | 58           | 193               |

|              | BNTST         | Test inverted bit                   | 59           | 193               |

|              | BNXOR         | Exclusive OR inverted bits          | 60           | 194               |

|              | BOR           | Logically OR bits                   | 61           | 194               |

|              | BSET          | Set bit                             | 64           | 196               |

|              | BTST          | Test bit                            | 65           | 196               |

|              | BTSTC         | Test bit & clear                    | 66           | 197               |

|              | BTSTS         | Test bit & set                      | 67           | 198               |

|              | BXOR          | Exclusive OR bits                   | 68           | 198               |

| Shift        | ROLC          | Rotate left with carry              | 126          | 274               |

|              | RORC          | Rotate right with carry             | 127          | 274               |

|              | ROT           | Rotate                              | 128          | 275               |

|              | SHA           | Shift arithmetic                    | 134          | 282               |

|              | SHANC         | Shift arithmetic                    | 135          | 284               |

|              | SHL           | Shift logical                       | 136          | 285               |

|              | SHLNC         | Shift logical                       | 137          | 288               |

| Arithmetic   | ABS           | Absolute value                      | 43           | 174               |

|              | ADC           | Add with carry                      | 44           | 174               |

|              | ADCF          | Add carry flag                      | 45           | 176               |

|              | ADD           | Add without carry                   | 46           | 176               |

|              | ADDX          | Add extend sigh without carry       | 48           | 183               |

### **Quick Reference by Function**

| Function   | Mnemonic | Content                         | See page for | See page for      |

|------------|----------|---------------------------------|--------------|-------------------|

|            |          |                                 | function     | instruction code/ |

|            |          |                                 |              | number of cycles  |

| Arithmetic | CLIP     | Clip                            | 69           | 199               |

|            | CMP      | Compare                         | 70           | 200               |

|            | CPMX     | Compare extended sigh           | 72           | 206               |

|            | DADC     | Decimal add with carry          | 73           | 206               |

|            | DADD     | Decimal add without carry       | 74           | 208               |

|            | DEC      | Decrement                       | 75           | 210               |

|            | DIV      | Signed divide                   | 76           | 210               |

|            | DIVU     | Unsigned divide                 | 77           | 212               |

|            | DIVX     | Singed divide                   | 78           | 213               |

|            | DSBB     | Decimal subtract with borrow    | 79           | 215               |

|            | DSUB     | Decimal subtract without borrow | 80           | 217               |

|            | EXTS     | Extend sign                     | 83           | 220               |

|            | EXTZ     | Extend zero                     | 84           | 222               |

|            | INC      | Increment                       | 88           | 225               |

|            | MAX      | Select maximum value            | 102          | 241               |

|            | MIN      | Select minimum value            | 103          | 243               |

|            | MUL      | Signed multiply                 | 109          | 257               |

|            | MULEX    | Multiple extend sign            | 110          | 260               |

|            | MULU     | Unsigned multiply               | 111          | 260               |

|            | NEG      | Two's complement                | 112          | 263               |

|            | RMPA     | Calculate sum-of-products       | 125          | 273               |

|            | SBB      | Subtract with borrow            | 130          | 277               |

|            | SUB      | Subtract without borrow         | 149          | 295               |

|            | SUBX     | Subtract extend without borrow  | 151          | 299               |

| Logical    | AND      | Logical AND                     | 50           | 186               |

|            | NOT      | Invert all bits                 | 114          | 264               |

|            | OR       | Logical OR                      | 115          | 264               |

|            | TST      | Test                            | 152          | 301               |

|            | XOR      | Exclusive OR                    | 157          | 304               |

| Jump       | ADJNZ    | Add & conditional jump          | 49           | 185               |

|            | SBJNZ    | Subtract & conditional jump     | 131          | 279               |

|            | JCnd     | Jump on condition               | 92           | 231               |

|            | JMP      | Unconditional jump              | 93           | 231               |

|            | JMPI     | Jump indirect                   | 94           | 233               |

|            | JMPS     | Jump to special page            | 95           | 234               |

|            | JSR      | Subroutine call                 | 96           | 235               |

|            | JSRI     | Indirect subroutine call        | 97           | 236               |

|            | JSRS     | Special page subroutine call    | 98           | 237               |

|            | RTS      | Return from subroutine          | 129          | 276               |

| String     | SCMPU    | String compare unequal          | 133          | 281               |

|            | SIN      | String input                    | 138          | 288               |

### **Quick Reference by Function**

| Function | Mnemonic      | Content                             | See page for | See page for      |

|----------|---------------|-------------------------------------|--------------|-------------------|

|          |               |                                     | function     | instruction code/ |

|          |               |                                     |              | number of cycles  |

| String   | SMOVB         | Transfer string backward            | 139          | 289               |

|          | SMOVF         | Transfer string forward             | 140          | 289               |

|          | SMOVU         | Transfer string                     | 141          | 290               |

|          | SOUT          | String output                       | 142          | 290               |

|          | SSTR          | Store string                        | 143          | 291               |

| Other    | BRK           | Debug interrupt                     | 62           | 195               |

|          | BRK2          | Debug interrupt 2                   | 63           | 195               |

|          | ENTER         | Build stack frame                   | 81           | 219               |

|          | EXITD         | Deallocate stack frame              | 82           | 219               |

|          | FCLR          | Clear flag register bit             | 85           | 223               |

|          | FREIT         | Fast return from interrupt          | 86           | 223               |

|          | FSET          | Set flag register bit               | 87           | 224               |

|          | INDEX Type    | Index                               | 89           | 225               |

|          | INT           | Interrupt by INT instruction        | 90           | 230               |

|          | INTO          | Interrupt on overflow               | 91           | 230               |

|          | LDC           | Transfer to control register        | 99           | 237               |

|          | LDCTX         | Restore context                     | 100          | 240               |

|          | LDIPL         | Set interrupt enable level          | 101          | 241               |

|          | NOP           | No operation                        | 113          | 263               |

|          | POPC          | Restore control register            | 118          | 267               |

|          | PUSHC         | Save control register               | 122          | 271               |

|          | REIT          | Return from interrupt               | 124          | 273               |

|          | STC           | Transfer from control register      | 144          | 291               |

|          | STCTX         | Save context                        | 145          | 293               |

|          | SC <i>cnd</i> | Store on condition                  | 132          | 280               |

|          | UND           | Interrupt for undefined instruction | 154          | 303               |

|          | WAIT          | Wait                                | 155          | 303               |

### **Quick Reference by Addressing (general instruction addressing)**

| Mnemonic  | Addr        |          |             |          |          |          |           |              |            |               |            |       |       |          | ing    |          |        |      |          |             |                |              |                 |              |          |          | See      | See page        |

|-----------|-------------|----------|-------------|----------|----------|----------|-----------|--------------|------------|---------------|------------|-------|-------|----------|--------|----------|--------|------|----------|-------------|----------------|--------------|-----------------|--------------|----------|----------|----------|-----------------|

|           |             |          |             |          |          |          |           |              |            |               |            |       |       |          |        |          |        |      |          |             |                |              |                 |              |          |          | page     | for             |

|           |             |          |             |          |          |          |           |              |            |               |            |       |       |          |        |          |        |      |          |             | _              |              | =               |              |          |          | for      | instruction     |

|           | 2R0         |          | 3R1         |          |          |          |           | FBJ          | _          | 3/FB          | _          |       |       |          |        |          |        |      |          |             | /FB]           | 듣            | B/FB            | =            |          |          | function | code<br>/number |

|           | 30/R        | R2/-     | 71/R        | R3/-     |          |          | [An]      | [SB/         | 6[An       | e[SE          | 4[An       | _     | _     | ω        | 16     | 24       | 32     |      |          | 3[An        | 3[SB           | l6[A         | <u> </u>        | 24[A         | 6]       | 4        |          | of cycles       |

|           | ROL/RO/R2R0 | R0H/R2/- | R1L/R1/R3R1 | R1H/R3/- | An       | [An]     | dsp:8[An] | dsp:8[SB/FB] | dsp:16[An] | dsp:16[SB/FB] | dsp:24[An] | abs16 | abs24 | #IMM8    | #IMM16 | #IMM24   | #IMM32 | #IMM | [[An]]   | [dsp:8[An]] | [dsp:8[SB/FB]] | [dsp:16[An]] | [dsp:16[SB/FB]] | [dsp:24[An]] | [abs16]  | [abs24]  |          | or oyoloo       |

| ABS       | √*2         | 1        | √*3         | 1        | 1        | <b>V</b> | 1         | 1            | 1          | 1             | 1          |       |       |          |        |          |        |      | 1        | 1           | 1              | 1            | 1               | 1            | 1        | <b>√</b> | 43       | 174             |

| ADC       | √*2         | 1        | √*3         | √        | <b>V</b> | √        | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      |          |             |                |              |                 |              |          |          | 44       | 174             |

| ADCF      | √*2         | 1        | √*3         | √        | <b>V</b> | √        | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     |          |        |          |        |      | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | 1            | <b>V</b> | <b>V</b> | 45       | 176             |

| ADD*1     | √           | 1        | √*3         | √        | <b>V</b> | <b>V</b> | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          | 1      | 1    | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | 1            | <b>V</b> | <b>V</b> | 46       | 176             |

| ADDX      | √*2         | √*4      | √*3         | √*5      | 1        | √        | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> |        |          |        |      | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | √            | <b>√</b> | <b>√</b> | 48       | 183             |

| ADJNZ*1   | √*2         | 1        | √*3         | √        | <b>V</b> | √        | 1         | √            | √          | <b>V</b>      | 1          | 1     | 1     |          |        |          |        | 1    |          |             |                |              |                 |              |          |          | 49       | 185             |

| AND       | √*2         | 1        | √*3         | √        | 1        | √        | 1         | 1            | √          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | √            | <b>V</b> | <b>V</b> | 50       | 186             |

| BITINDEX  | √*2         | 1        | √*3         | √        | 1        | √        | 1         | 1            | √          | <b>V</b>      | 1          | 1     | 1     |          |        |          |        |      |          |             |                |              |                 |              |          |          | 54       | 189             |

| CLIP      | √*2         | 1        | √*3         | √        | 1        | √        | 1         | 1            | <b>V</b>   | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      |          |             |                |              |                 |              |          |          | 69       | 199             |

| CMP       | √           | 1        | 1           | √        | 1        | √        | 1         | 1            | <b>V</b>   | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          | 1      | 1    | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | √            | <b>V</b> | <b>V</b> | 70       | 200             |

| CMPX      | √*6         | 1        | √*7         | √        | √        | √        | 1         | 1            | √          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> |        |          |        |      | <b>V</b> | 1           | <b>V</b>       | √            | 1               | √            | √        | <b>V</b> | 72       | 206             |

| DADC      | √*2         | 1        | √*3         | √        | 1        | √        | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      |          |             |                |              |                 |              |          |          | 73       | 206             |

| DADD      | √*2         | 1        | √*3         | √        | √        | √        | √         | 1            | 1          | <b>V</b>      | √          | 1     | 1     | √        | 1      |          |        |      |          |             |                |              |                 |              |          |          | 74       | 208             |

| DEC       | √           | 1        | 1           | √        | √        | √        | √         | √            | √          | <b>V</b>      | √          | 1     | 1     |          |        |          |        |      | √        | 1           | √              | √            | 1               | √            | √        | √        | 75       | 210             |

| DIV       | 1           | 1        | 1           | √        | 1        | √        | 1         | 1            | 1          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      | <b>V</b> | 1           | <b>V</b>       | <b>V</b>     | 1               | √            | <b>√</b> | <b>V</b> | 76       | 210             |

| DIVU      | 1           | 1        | 1           | √        | √        | √        | 1         | 1            | √          | <b>V</b>      | 1          | 1     | 1     | <b>V</b> | 1      |          |        |      | <b>V</b> | 1           | <b>V</b>       | √            | 1               | √            | √        | <b>V</b> | 77       | 212             |

| DIVX      | 1           | 1        | 1           | 1        | 1        | √        | 1         | √            | 1          | 1             | √          | 1     | √     | 1        | 1      |          |        |      | <b>V</b> | 1           | <b>V</b>       | 1            | 1               | 1            | 1        | <b>V</b> | 78       | 213             |

| DSBB      | √*2         | 1        | √*3         | 1        | 1        | √        | 1         | √            | 1          | 1             | √          | 1     | √     | 1        | 1      |          |        |      | <b>√</b> | 1           | <b>V</b>       | 1            | 1               | 1            | 1        | <b>V</b> | 79       | 215             |

| DSUB      | √*2         | 1        | √*3         | 1        | 1        | √        | 1         | √            | 1          | 1             | √          | 1     | √     | 1        | 1      |          |        |      | <b>V</b> | 1           | <b>V</b>       | 1            | 1               | 1            | 1        | <b>V</b> | 80       | 217             |

| ENTER     |             |          |             |          |          |          |           |              |            |               |            |       |       |          |        | <b>V</b> |        |      |          |             |                |              |                 |              |          |          | 81       | 219             |

| EXTS      | √*2         | 1        | √*3         | 1        | 1        | 1        | 1         | 1            | 1          | 1             | <b>V</b>   | 1     | 1     |          |        |          |        |      |          |             |                |              |                 |              |          |          | 83       | 220             |

| EXTZ      | √*2         | 1        | √*3         | 1        | 1        | √        | 1         | <b>V</b>     | <b>V</b>   | 1             | 1          | 1     | 1     |          |        |          |        |      |          |             |                |              |                 |              |          |          | 84       | 222             |

| INC       | √*2         | 1        | √*3         | 1        | 1        | √        | 1         | <b>V</b>     | √          | 1             | 1          | 1     | 1     |          |        |          |        |      | <b>V</b> | 1           | √              | <b>V</b>     | 1               | √            | 1        | <b>V</b> | 88       | 225             |

| INDEXType | √*2         | 1        | √*3         | √        | <b>V</b> | √        | √         | 1            | √          | <b>V</b>      | 1          | 1     | 1     |          |        |          |        |      |          |             |                |              |                 |              |          |          | 89       | 225             |

<sup>\*1</sup> Has special instruction addressing.

<sup>\*2</sup> Only R0L/R0 can be selected.

<sup>\*3</sup> Only R1L/R1 can be selected.

<sup>\*4</sup> Only R0L can be selected.

<sup>\*5</sup> Only R0H can be selected.

<sup>\*6</sup> Only R1L can be selected.

<sup>\*7</sup> Only R1H can be selected.

### **Quick Reference by Addressing (general instruction addressing)**

| Mnemonic | ,g          |          |             |          |          |          |           |              |            |               |            |          |          |          | inc      | 1        |        |          |        |             |                | See          | See page        |              |         |          |          |                   |

|----------|-------------|----------|-------------|----------|----------|----------|-----------|--------------|------------|---------------|------------|----------|----------|----------|----------|----------|--------|----------|--------|-------------|----------------|--------------|-----------------|--------------|---------|----------|----------|-------------------|

|          |             |          |             |          |          |          |           |              |            |               |            |          |          |          |          |          |        |          |        |             |                |              |                 |              |         |          | page     | for               |

|          |             |          |             |          |          |          |           |              |            |               |            |          |          |          |          |          |        |          |        |             |                |              | =               |              |         |          | for      | instruction       |

|          | 2R0         |          | 3R1         |          |          |          |           | FB.          | _          | %FB]          | _          |          |          |          |          |          |        |          |        |             | /FB]]          | 듣            | 3/FB            | 듣            |         |          | function |                   |

|          | 30/R        | R2/-     | 71/R        | R3/-     |          |          | [An]      | [SB/         | 6[An       | e[SE          | 4[An       | _        |          | ω        | 16       | 24       | 32     |          |        | 3[An]       | 3[SB)          | l6[Aı        | <u> </u>        | 24[Aı        | [9      | 4        |          | /number of cycles |

|          | ROL/RO/R2R0 | R0H/R2/- | R1L/R1/R3R1 | R1H/R3/- | An       | [An]     | dsp:8[An] | dsp:8[SB/FB] | dsp:16[An] | dsp:16[SB/FB] | dsp:24[An] | abs16    | abs24    | #IMM8    | #IMM16   | #IMM24   | #IMM32 | #IMM     | [[An]] | [dsp:8[An]] | [dsp:8[SB/FB]] | [dsp:16[An]] | [dsp:16[SB/FB]] | [dsp:24[An]] | [abs16] | [abs24]  |          | oi cycles         |

| INT      |             |          |             |          |          |          |           |              |            |               |            |          |          |          |          |          |        | 1        |        |             |                |              |                 |              |         |          | 90       | 230               |

| JMP*1    |             |          |             |          |          |          |           |              |            |               |            |          | <b>V</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 93       | 231               |

| JMPI*1   | √*2         | √*3      | √*4         | √*5      | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | <b>V</b>      | <b>V</b>   | 1        | <b>V</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 94       | 233               |

| JMPS     |             |          |             |          |          |          |           |              |            |               |            |          |          |          |          | <b>V</b> |        |          |        |             |                |              |                 |              |         |          | 95       | 234               |

| JSRI     | √*2         | √*3      | √*4         | √*5      | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>√</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 97       | 236               |

| JSRS     |             |          |             |          |          |          |           |              |            |               |            |          |          | √        |          |          |        |          |        |             |                |              |                 |              |         |          | 98       | 237               |

| LDC*1    | √*2         | √*3      | √*4         | √*5      | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>√</b> |          | <b>V</b> | √        |        |          |        |             |                |              |                 |              |         |          | 99       | 237               |

| LDIPL    |             |          |             |          |          |          |           |              |            |               |            |          |          |          |          |          |        | <b>V</b> |        |             |                |              |                 |              |         |          | 101      | 241               |

| MAX      | √*6         | 1        | √*7         | <b>V</b> | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>√</b> | 1        | <b>V</b> |          |        |          |        |             |                |              |                 |              |         |          | 102      | 241               |

| MIN      | √*6         | 1        | √*7         | <b>V</b> | √        | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>V</b> | <b>V</b> | <b>V</b> |          |        |          |        |             |                |              |                 |              |         |          | 103      | 243               |

| MOV*1    | √           | 1        | <b>V</b>    | 1        | √        | √        | <b>V</b>  | 1            | √          | √             | √          | 1        | √        | 1        | <b>V</b> | √        | 1      | <b>V</b> | 1      | √           | √              | √            | 1               | <b>√</b>     | 1       | √        | 104      | 245               |

| MOVA     | √*8         |          | √*9         |          | <b>V</b> |          | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>V</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 106      | 254               |

| MOVDir   | √*10        | √*11     | √*12        | √*13     |          | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | √             | 1          | 1        | <b>V</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 107      | 255               |

| MOVX     | √*8         |          | √*9         |          | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | <b>V</b>      | 1          | 1        | <b>V</b> | 1        |          |          |        |          | 1      | √           | 1              | <b>V</b>     | 1               | <b>V</b>     | 1       | <b>V</b> | 108      | 257               |

| MUL      | 1           | 1        | 1           |          | <b>V</b> | <b>V</b> | <b>V</b>  | 1            | <b>V</b>   | <b>V</b>      | <b>V</b>   | 1        | <b>√</b> | <b>V</b> | <b>V</b> |          |        |          | 1      | <b>√</b>    | <b>V</b>       | <b>V</b>     | 1               | <b>V</b>     | 1       | <b>V</b> | 109      | 257               |

| MULEX    |             |          |             | √*5      | <b>V</b> | √        | <b>V</b>  | 1            | √          | V             | √          | 1        | √        |          |          |          |        |          | √      | √           | √              | √            | √               | √            | 1       | √        | 110      | 260               |

| MULU     | 1           | 1        | 1           | 1        | <b>V</b> |          | <b>V</b>  | 1            | 1          |               | <b>V</b>   | 1        | 1        | 1        | 1        |          |        |          | 1      | 1           | 1              | <b>V</b>     | 1               | <b>V</b>     | 1       | <b>V</b> | 111      | 260               |

| NEG      | √*6         | 1        | √*7         | 1        | <b>V</b> |          | <b>V</b>  | 1            | 1          |               | <b>V</b>   | 1        | 1        |          |          |          |        |          | 1      | 1           | 1              | <b>V</b>     | 1               | <b>V</b>     | 1       | <b>V</b> | 112      | 263               |

| NOT      | √*6         | 1        | √*7         | 1        | <b>V</b> |          | <b>V</b>  | 1            | 1          |               | <b>V</b>   | 1        | 1        |          |          |          |        |          | 1      | 1           | 1              | <b>V</b>     | 1               | <b>V</b>     | 1       | <b>V</b> | 114      | 264               |

| OR       | √*6         | 1        | √*7         | 1        | √        | 1        | <b>V</b>  | 1            | <b>V</b>   | V             | √          | 1        | 1        | 1        | <b>V</b> |          |        |          | 1      | <b>V</b>    |                | <b>V</b>     | √               | <b>V</b>     | 1       | √        | 115      | 264               |

| POP      | √*6         | 1        | √*7         | √        | <b>V</b> | V        | <b>V</b>  | 1            | <b>V</b>   | V             | √          | <b>V</b> | √        |          |          |          |        |          | √      | <b>V</b>    | 1              | V            | √               | <b>V</b>     | 1       | √        | 117      | 267               |

| POPM*1   | V           | 1        | √           | <b>V</b> |          |          |           |              |            |               |            |          |          |          |          |          |        |          |        |             |                |              |                 |              |         |          | 119      | 268               |

| PUSH     | V           | 1        | <b>V</b>    | 1        | <b>V</b> | 1        | 1         | 1            | 1          | 1             |            | 1        | <b>V</b> | 1        | 1        |          | 1      |          | 1      | 1           | 1              | 1            | 1               | 1            | 1       | <b>V</b> | 120      | 269               |

| PUSHA    |             |          |             |          |          |          | <b>V</b>  | 1            | <b>V</b>   | V             | √          | <b>V</b> | <b>√</b> |          |          |          |        |          |        |             |                |              |                 |              |         |          | 121      | 271               |

- \*1 Has special instruction addressing.

- \*2 Only R0/R2R0 can be selected.

- \*3 Only R2 can be selected.

- \*4 Only R1/R3R1 can be selected.

- \*5 Only R3 can be selected.

- \*6 Only R0L/R0 can be selected.

- \*7 Only R1L/R1 can be selected.

- \*8 Only R2R0 can be selected.

- \*9 Only R3R1 can be selected.

- \*10 Only R0L can be selected.

- \*11 Only R0H can be selected.

- \*12 Only R1L can be selected.

- \*13 Only R1H can be selected.

#### **Quick Reference by Addressing (general instruction addressing)**

| Mnemonic |             |          |             |          |          |      |           |              |            |               |            | Ac    | ldre  | ess   | ing    |        |        |      |        |             |                |              |                 |              |          |          | See                     | See page                                           |

|----------|-------------|----------|-------------|----------|----------|------|-----------|--------------|------------|---------------|------------|-------|-------|-------|--------|--------|--------|------|--------|-------------|----------------|--------------|-----------------|--------------|----------|----------|-------------------------|----------------------------------------------------|

|          | ROL/RO/R2R0 | R0H/R2/- | R1L/R1/R3R1 | R1H/R3/- | An       | [An] | dsp:8[An] | dsp:8[SB/FB] | dsp:16[An] | dsp:16[SB/FB] | dsp:24[An] | abs16 | abs24 | #IMM8 | #IMM16 | #IMM24 | #IMM32 | #IMM | [[An]] | [dsp:8[An]] | [dsp:8[SB/FB]] | [dsp:16[An]] | [dsp:16[SB/FB]] | [dsp:24[An]] | [abs16]  | [abs24]  | page<br>for<br>function | for<br>instruction<br>code<br>/number<br>of cycles |

| PUSHM*1  | √           | 1        | √           | √        |          |      |           |              |            |               |            |       |       |       |        |        |        |      |        |             |                |              |                 |              |          |          | 123                     | 272                                                |

| ROLC     | √*2         | 1        | √           | √*3      | 1        | √    | √         | √            | √          | √             | √          | 1     | 1     |       |        |        |        |      | √      | 1           | √              | 1            | √               | √            | √        | √        | 126                     | 274                                                |

| RORC     | √*2         | 1        | √           | √*3      | 1        | √    | √         | √            | √          | √             | √          | √     | √     |       |        |        |        |      | √      | 1           | √              | √            | √               | √            | √        | √        | 127                     | 274                                                |

| ROT      | √*2         | 1        | √           | √*3      | 1        | √    | √         | √            | √          | √             | √          | √     | 1     |       |        |        |        | √    | √      | 1           | √              | √            | √               | √            | √        | √        | 128                     | 275                                                |

| SBB      | √*2         | 1        | √           | √*3      | 1        | √    | √         | √            | √          | √             | $\sqrt{}$  | 1     | 1     | √     | √      |        |        |      |        |             |                |              |                 |              |          |          | 130                     | 277                                                |

| SBJNZ*1  | √*2         | 1        | √           | √*3      | 1        | √    | √         | √            | √          | √             |            | 1     | 1     |       |        |        |        | √    |        |             |                |              |                 |              |          |          | 131                     | 279                                                |

| SCCnd    | √*4         | √*5      | √*6         | √*7      | 1        | √    | √         | √            | √          | √             |            | 1     | 1     |       |        |        |        |      | √      | 1           | √              | √            | √               | √            | √        | √        | 132                     | 280                                                |

| SHA      | √           | 1        | √           | √        | 1        | √    | √         | √            | √          | √             |            | 1     | 1     | √     |        |        |        | √    | √      | 1           | √              | √            | √               | √            | √        | √        | 134                     | 282                                                |

| SHANC    | √*12        |          | √*13        |          | √        | √    | √         | √            | √          | √             | $\sqrt{}$  |       | √     | √     |        |        |        |      | √      | √           |                | √            | √               | √            | √        | √        | 135                     | 284                                                |

| SHL      |             | 1        |             | <b>V</b> |          | √    |           | <b>√</b>     | 1          | √             | $\sqrt{}$  |       |       | √     |        |        |        | √    | √      |             |                | 1            | √               |              |          | <b>√</b> | 136                     | 285                                                |

| SHLNC    | √*12        |          | √*13        |          |          | √    | √         | √            | 1          | √             |            |       |       | √     |        |        |        |      | √      |             |                | 1            | √               |              |          | <b>√</b> | 137                     | 288                                                |

| STC*1    | √*4         | √*5      | √*6         | √*7      | <b>V</b> | √    | √         | √            | <b>V</b>   | √             | <b>√</b>   | 1     | 1     |       |        |        |        |      |        |             |                |              |                 |              |          |          | 144                     | 291                                                |

| STCTX*1  | √           | 1        | <b>V</b>    | √        |          |      |           |              |            |               |            |       |       |       |        |        |        |      |        |             |                |              |                 |              |          |          | 145                     | 293                                                |

| STNZ     | √*2         | 1        |             | √*3      |          | √    | √         | √            | 1          | √             |            |       |       | √     | √      |        |        |      | √      |             |                | 1            | <b>V</b>        |              |          | <b>√</b> | 146                     | 293                                                |

| STZ      | √*2         | 1        | 1           | √*3      | 1        | √    | 1         | <b>V</b>     | 1          | V             | <b>V</b>   | 1     | 1     | √     | 1      |        |        |      | √      | 1           | <b>V</b>       | 1            | <b>V</b>        | 1            | <b>V</b> | √        | 147                     | 294                                                |

| STZX     | √*2         | 1        | 1           | √*3      | 1        | √    | 1         | <b>V</b>     | 1          | V             | <b>V</b>   | 1     | 1     | V     | 1      |        |        |      | √      | 1           | <b>V</b>       | 1            | <b>V</b>        | 1            | <b>V</b> | <b>V</b> | 148                     | 294                                                |

| SUB      | V           | 1        | 1           | <b>V</b> | 1        | 1    | <b>V</b>  | <b>V</b>     | 1          | √             | <b>V</b>   | 1     | 1     | V     | √      |        | √      |      | V      | 1           | <b>V</b>       | <b>V</b>     | <b>V</b>        | <b>V</b>     | √        | <b>V</b> | 149                     | 295                                                |

| SUBX     | √*8         | √*9      | √*10        | √*11     | V        | 1    | 1         | 1            | 1          | 1             | <b>√</b>   | V     | 1     | √     |        |        |        |      | √      | V           |                | 1            | <b>V</b>        | 1            | <b>V</b> | <b>V</b> | 151                     | 299                                                |

| TST      | √*2         | 2 √      | 1           | √*3      | 1        | 1    | √         | √            | 1          | 1             | √          | V     | 1     | √     | 1      |        |        |      |        |             |                |              |                 |              |          |          | 152                     | 301                                                |

| XCHG     | √*2         | √        | 1           | √*3      | 1        | √    | √         | 1            | √          | V             | √          | 1     | 1     |       |        |        |        |      | √      | 1           | 1              | √            | 1               | √            | 1        | √        | 156                     | 304                                                |

| XOR      | √*2         | √        | 1           | √*3      |          | 1    | √         | √            | 1          | √             |            |       | √     | √     | √      |        |        |      | √      | 1           | 1              | √            | 1               | √            | √        | √        | 157                     | 304                                                |

<sup>\*1</sup> Has special instruction addressing.

\*12 Only R2R0 can be selected.

\*13 Only R3R1 can be selected.

<sup>\*2</sup> Only R0L/R0 can be selected.

<sup>\*3</sup> Only R1L/R1 can be selected.

<sup>\*4</sup> Only R0 can be selected.

<sup>\*5</sup> Only R2 can be selected.

<sup>\*6</sup> Only R1 can be selected.

<sup>\*7</sup> Only R3 can be selected.

<sup>\*8</sup> Only R0L/R2R0 can be selected.

<sup>\*9</sup> Only R0H can be selected.

<sup>\*10</sup> Only R1L/R3R1 can be selected.

<sup>\*11</sup> Only R1H can be selected.

### **Quick Reference by Addressing (special instruction addressing)**

| Mnemonic     |          |       |         |     |          | Add     | dres | sing      |           |           |           |           |           | See page     | See page                                           |

|--------------|----------|-------|---------|-----|----------|---------|------|-----------|-----------|-----------|-----------|-----------|-----------|--------------|----------------------------------------------------|

|              | label    | SB/FB | ISP/USP | FLG | INTB     | SVP/VCT | SVF  | DMD0/DMD1 | DCT0/DCT1 | DRC0/DRC1 | DMA0/DMA1 | DRA0/DRA1 | DSA0/DSA1 | for function | for<br>instruction<br>code<br>/number of<br>cycles |

| ADD*1        |          |       | 1       |     |          |         |      |           |           |           |           |           |           | 46           | 176                                                |

| ADJNZ*1      |          |       |         |     |          |         |      |           |           |           |           |           |           | 49           | 185                                                |

| J <i>Cnd</i> |          |       |         |     |          |         |      |           |           |           |           |           |           | 92           | 231                                                |

| JMP*1        |          |       |         |     |          |         |      |           |           |           |           |           |           | 93           | 231                                                |

| JSR*1        | 1        |       |         |     |          |         |      |           |           |           |           |           |           | 96           | 235                                                |

| LDC*1        |          | 1     | 1       | 1   | 1        | 1       | 1    | 1         | 1         | √         | 1         | 1         | <b>√</b>  | 99           | 237                                                |

| POPC         |          | 1     | 1       | 1   | 1        | 1       | 1    | 1         | 1         |           |           |           |           | 118          | 267                                                |

| POPM*1       |          | 1     |         |     |          |         |      |           |           |           |           |           |           | 119          | 268                                                |

| PUSHC        |          | 1     | 1       | 1   | 1        | 1       | 1    | 1         | 1         |           |           |           |           | 122          | 271                                                |

| PUSHM*1      |          | 1     |         |     |          |         |      |           |           |           |           |           |           | 123          | 272                                                |

| SBJNZ*1      | <b>V</b> |       |         |     |          |         |      |           |           |           |           |           |           | 131          | 279                                                |

| STC*1        |          | √     | √       | √   | <b>√</b> | √       | 1    | √         | √         | √         | √         | √         | <b>V</b>  | 144          | 291                                                |

<sup>\*1</sup> Has general instruction addressing.

### **Quick Reference by Addressing (bit instruction addressing)**

| Mnemonic      |             | Addressing  |           |          |                 |                    |                 |                    | See page        | See page    |             |                 |              |                                                    |

|---------------|-------------|-------------|-----------|----------|-----------------|--------------------|-----------------|--------------------|-----------------|-------------|-------------|-----------------|--------------|----------------------------------------------------|

|               | bit,R0L/R0H | bit,R1L/R1H | bit,An    | bit,[An] | bit,base:11[An] | bit,base:11[SB/FB] | bit,base:19[An] | bit,base:19[SB/FB] | bit,base:27[An] | bit,base:27 | bit,base:19 | U/I/O/B/S/Z/D/C | for function | for<br>instruction<br>code<br>/number of<br>cycles |

| BAND          | 1           | 1           | 1         | √        | <b>V</b>        | 1                  | <b>V</b>        | V                  | <b>V</b>        | <b>V</b>    | 1           |                 | 52           | 188                                                |

| BCLR          | √           | √           |           | √        |                 | $\sqrt{}$          | √               | $\sqrt{}$          | <b>√</b>        | √           | $\sqrt{}$   |                 | 53           | 188                                                |

| BM <i>Cnd</i> | √           | √           | √         | √        | $\sqrt{}$       | $\sqrt{}$          | √               |                    |                 | √           | $\sqrt{}$   |                 | 55           | 190                                                |

| BNAND         |             | √           | √         | √        | $\sqrt{}$       | $\sqrt{}$          | √               |                    | $\checkmark$    | √           | $\sqrt{}$   |                 | 56           | 192                                                |

| BNOR          | √           | √           | $\sqrt{}$ | √        | $\sqrt{}$       | $\sqrt{}$          |                 | $\sqrt{}$          |                 | √           | $\sqrt{}$   |                 | 57           | 192                                                |

| BNOT          | √           | √           | √         | √        | $\sqrt{}$       | $\sqrt{}$          | √               | $\sqrt{}$          | <b>√</b>        | √           | $\sqrt{}$   |                 | 58           | 193                                                |

| BNTST         | √           | √           | √         | <b>V</b> |                 | <b>√</b>           | <b>√</b>        | <b>√</b>           | $\checkmark$    | √           | $\sqrt{}$   |                 | 59           | 193                                                |

| BNXOR         | 1           | √           | √         | √        |                 | $\sqrt{}$          | <b>V</b>        | <b>√</b>           |                 | √           | √           |                 | 60           | 194                                                |

| BOR           | √           | √           | √         | √        | $\sqrt{}$       | $\sqrt{}$          | √               | $\sqrt{}$          | <b>√</b>        | √           | $\sqrt{}$   |                 | 61           | 194                                                |

| BSET          | √           | √           | √         | 1        | √               | √                  |                 | √                  |                 | 1           | √           |                 | 64           | 196                                                |

| BTST          | √           | √           | √         | 1        | √               | √                  |                 | √                  |                 | 1           | √           |                 | 65           | 196                                                |

| BTSTC         | 1           | 1           | √         | 1        | √               | $\sqrt{}$          | √               | V                  | <b>V</b>        | √           | <b>V</b>    |                 | 66           | 197                                                |

| BTSTS         | 1           | 1           | 1         | 1        | √               | 1                  | √               | V                  | <b>V</b>        | √           | V           |                 | 67           | 198                                                |

| BXOR          | 1           | 1           | √         | 1        | $\sqrt{}$       | 1                  |                 | V                  |                 | √           | V           |                 | 68           | 198                                                |

| FCLR          |             |             |           |          |                 |                    |                 |                    |                 |             |             | V               | 85           | 223                                                |

| FSET          |             |             |           |          |                 |                    |                 |                    |                 |             |             | √               | 87           | 224                                                |

# Chapter 1

## Overview

- 1.1 Features of M32C/80 Series

- 1.2 Address Space

- 1.3 Register Configuration

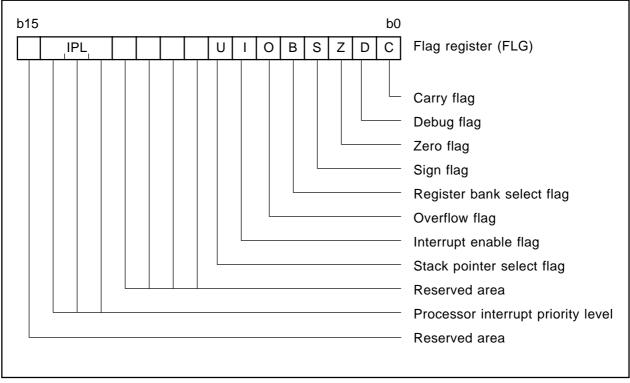

- 1.4 Flag Register (FLG)

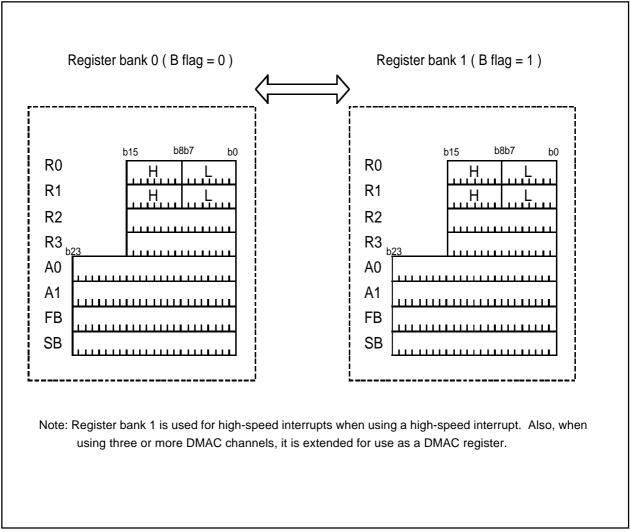

- 1.5 Register Bank

- 1.6 Internal State after Reset

- 1.7 Data Types

- 1.8 Data Arrangement

- 1.9 Instruction Format

- 1.10 Vector Table

#### 1.1 Features of M32C/80 Series

The M32C/80 Series is a single-chip MCU developed for built-in applications where the MCU is built into applications equipment.

The M32C/80 Series supports instructions suitable for the C language with frequently used instructions arranged in one- byte op-code. Therefore, it allows you for efficient program development with few memory capacity regardless of whether you are using the assembly language or C language. Furthermore, some instructions can be executed in one clock cycle, making fast arithmetic processing possible.

Its instruction set consists of 108 discrete instructions matched to the M32C's abundant addressing modes. This powerful instruction set allows to perform register-register, register-memory, and memory-memory operations, as well as arithmetic/logic operations on bits and 4-bit data.

M32C/80 Series models incorporate a multiplier, allowing for high-speed computation.

#### Features of M32C/80 Series

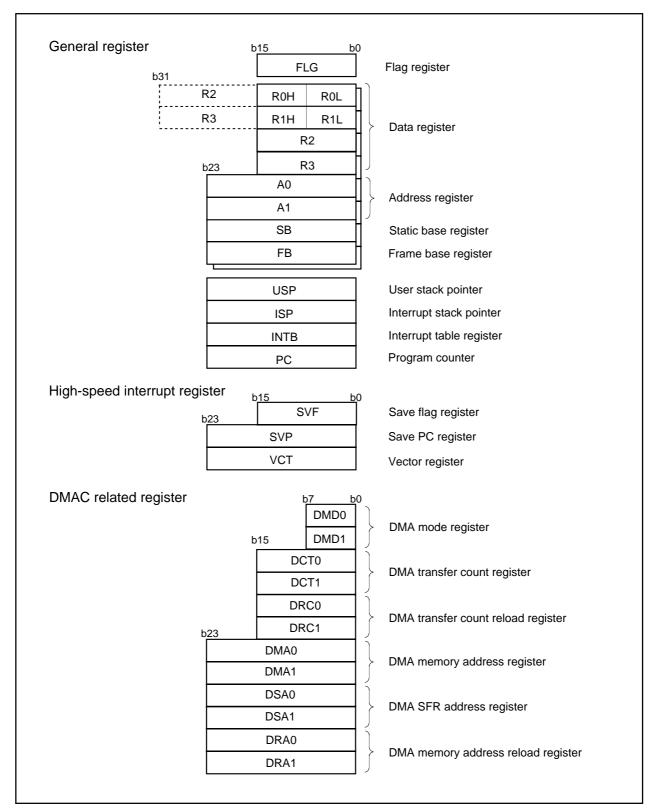

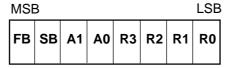

#### Register configuration

Data registers : Four 16-bit registers (of which two registers can be used as 8-bit registers, or two

registers are combined and can be used as 32-bit registers)

Address registers : Two 24-bit registers

Base registers : Two 24-bit registers

#### Versatile instruction set

C language-suited instructions (stack frame manipulation) : ENTER, EXITD, etc.

Register and memory-indiscriminated instructions : MOV, ADD, SUB, etc.

Powerful bit manipulate instructions : BNOT, BTST, BSET, etc.

4-bit transfer instructions : MOVLL, MOVHL, etc.

Frequently used 1-byte instructions : MOV, ADD, SUB, JMP, etc.

High-speed 1-cycle instructions : MOV, ADD, SUB, etc.

#### 16M-byte linear address area

Relative jump instructions matched to distance of jump

#### Fast instruction execution time

Shortest 1-cycle instructions : 108 instructions include 39 1-cycle instructions.

#### Speed performance (types incorporating a multiplier, operating at 32 MHz)

|                                               | Cycle | <b>Execution Time</b> |

|-----------------------------------------------|-------|-----------------------|

| Register-register transfer                    | 1     | 31.3 ns               |

| Register-memory transfer                      | 1     | 31.3 ns               |

| Register-register addition/subtraction        | 1     | 31.3 ns               |

| 8 bits x 8 bits register-register operation   | 3     | 93.8 ns               |

| 16 bits x 16 bits register-register operation | 3     | 93.8 ns               |

| 16 bits / 8 bits register-register operation  | 18    | 562.5 ns              |

| 32 bits / 16 bits register-register operation | 18    | 562.5 ns              |

### 1.2 Address Space

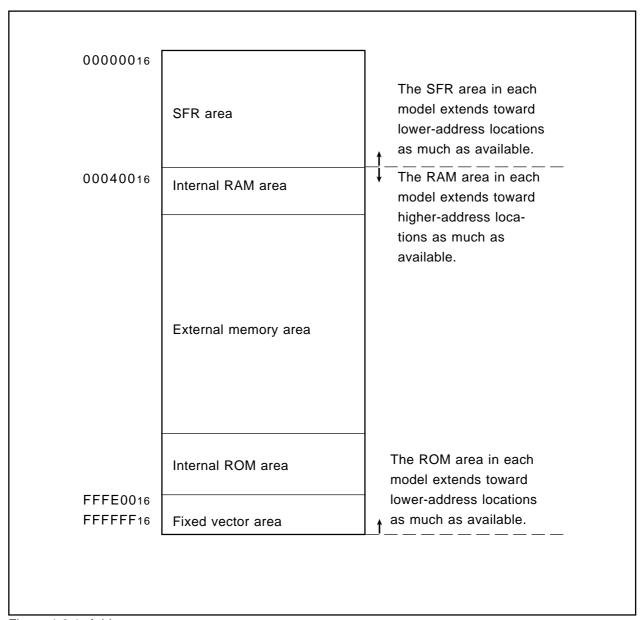

Fig. 1.2.1 shows an address space.

Addresses 00000016 through 0003FF16 make up an SFR (special function register) area. In individual models of the M32C/80 Series, the SFR area extends from 0003FF16 toward lower addresses.

Addresses from 00040016 on make up a memory area. In individual models of the M32C/80 Series, a RAM area extends from address 00040016 toward higher addresses, and a ROM area extends from FFFFF16 toward lower addresses. Addresses FFFE0016 through FFFFF16 make up a fixed vector area.

Figure 1.2.1 Address area

### 1.3 Register Configuration

Figure 1.3.1 shows the CPU registers. The register bank is comprised of eight registers (R0, R1, R2, R3, A0, A1, FB, and SB) out of 28 CPU registers. There are two sets of register banks.

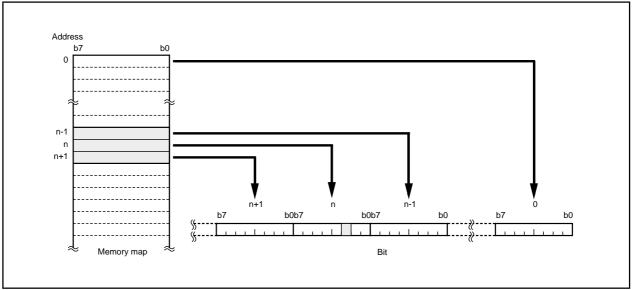

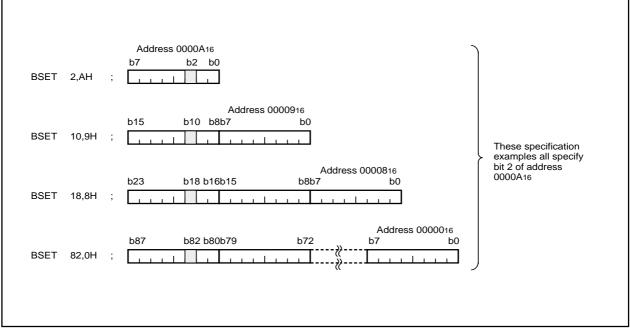

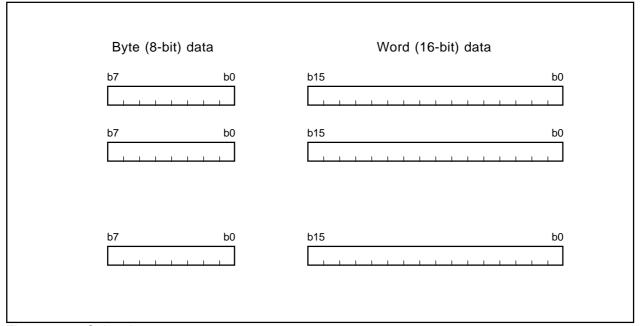

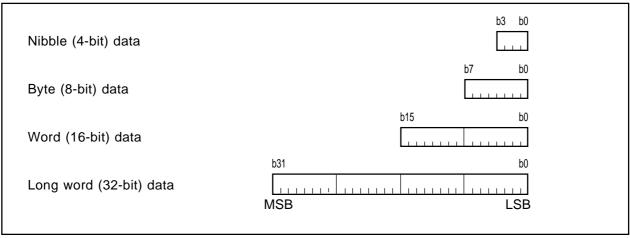

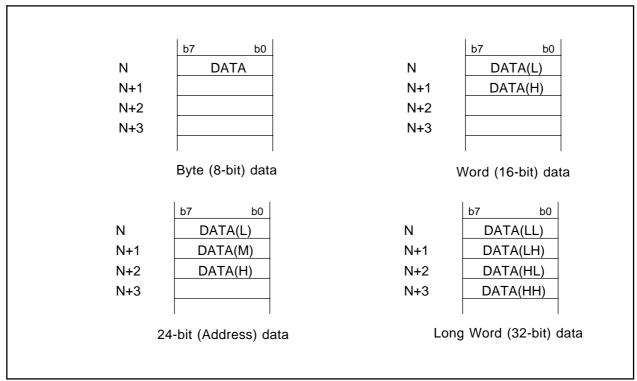

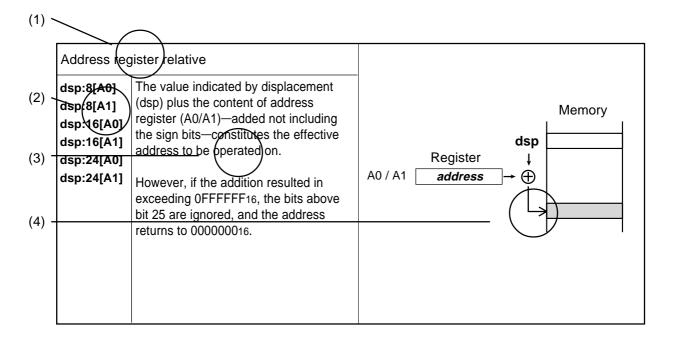

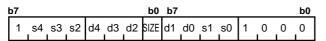

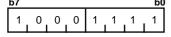

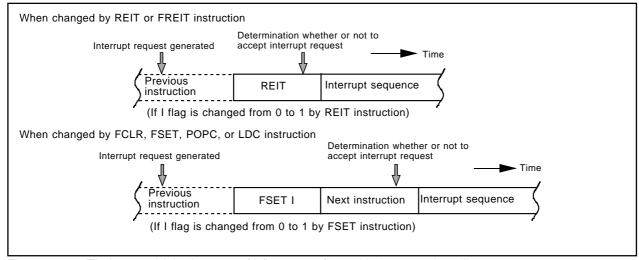

Figure 1.3.1 CPU register configuration